极薄绝缘层与二维 (2D) 半导体的有效集成,可以制造出厚度低于 1 纳米、电容可与 SiO 2媲美的 2D 晶体管。这些晶体管反过来可以帮助提高电子设备的性能并降低功耗。

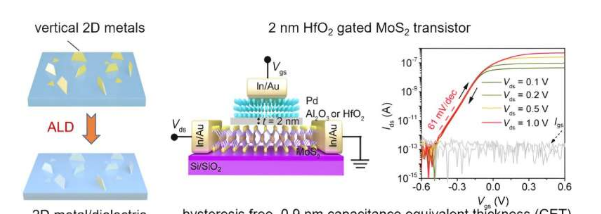

中国南开大学的研究人员最近介绍了一种合成单晶金属纳米片的新方法,这种纳米片可以轻松转移到二维基板上。《自然电子学》杂志上的一篇论文概述了这种方法,该方法已成功用于沉积基于 Al 2 O 3或 HfO 2的 2 纳米厚电介质,用于高性能顶栅晶体管。

论文通讯作者吴金雄告诉 Tech Xplore:“我们一开始的目标是开发2D Cu 2 O 的化学气相沉积(CVD) 合成策略,这是一种p型高迁移率 2D 半导体。”

“然而,我们使用 CuCl 和 Bi 2 O 3作为反应前体,得到的却是单质 Cu 金属。此外,通过改变金属氯化物的类型,我们还可以得到其他二维金属,例如 Pd 和 Au。”

在查阅先前的文献时,吴和他的同事发现,基于 Pd 和 Au 的二维金属尚未使用 CVD 合成,而 CVD 是一种常用于在基底上生产薄膜或材料的工艺。有趣的是,他们还意识到几乎所有的二维金属纳米片都具有原子级平坦的表面,并且可以在基底上垂直生长。

“我一直在问自己和我的学生‘我们能用这些知识做什么?’”吴说。“就在我们准备放弃这个项目的时候,鳍片场效应晶体管的配置给了我启发。

“如果我们能够将垂直生长的二维金属与原子层沉积(ALD)电介质结合在一起,就可以避免ALD技术与二维半导体之间的兼容性问题,以及在超薄电介质上沉积顶栅电极的破坏性步骤,为制造具有亚纳米电容等效厚度的二维场效应晶体管(FET)提供了一条途径。”

为了整合金属纳米片和介电材料,吴和他的学生直接在垂直生长的二维金属上沉积了原子级薄而平坦的介电材料,即 Al 2 O 3和 HfO 2。与通常用作晶体管通道半导体的二维过渡金属硫化物二硫化钼 (MoS 2 ) 不同,二维金属具有与 ALD 技术兼容的表面。在 ALD 生长之后,可以使用形成范德华界面的一步法将金属/氧化物堆栈与二维半导体集成。

该研究团队最近的研究介绍了一种基于二维金属和原子层沉积电介质制造二维晶体管的极具前景的方法。他们提出的策略需要使用超光滑垂直二维金属来实现超薄高κ氧化物的高质量 ALD 生长,以及随后的金属/氧化物堆栈的一步范德华集成。

吴说:“我们的策略不仅解决了 ALD 技术与 2D 半导体之间的不兼容问题,而且还可以避免在超薄电介质上进行顶栅电极沉积工艺的破坏性步骤,从而使得将无种子层 2D FET 的 CET 值缩小到亚纳米的巨大挑战成为可能。”

作为研究的一部分,研究人员使用他们提出的 CVD 策略创建了基于 Al 2 O 3或 HfO 2的 2 纳米厚的电介质,然后将其用于制造顶栅晶体管。在初步测试中,最终的晶体管获得了令人满意的结果,漏电流为 10 − 6 A cm − 2,工作电压低至 0.45 V 左右,磁滞低于 1 mV。

“我们认为,Bi 2 O 3辅助 CVD 生长方法的开发是 2D 材料 CVD 生长领域的一项重要进步,因为它能够合成一些使用传统方法难以合成的新型 2D 材料,”吴补充道。“我们现在计划实现晶圆级制造无磁滞 2D 晶体管,电容等效厚度低于 1 纳米。”