使用可扩展技术进行掺杂的基于碳纳米管的MOSFET

近年来,电子工程师一直在尝试寻找有助于缩小晶体管尺寸而不影响其性能和能效的材料。低维半导体、空间维度少于三个的固态超导材料可以帮助实现这一目标。

在低维半导体材料中,一维(1D)碳纳米管是特别有希望缩短晶体管内部栅极长度的材料。尽管如此,大多数提出的掺杂这些材料并控制其内部极性的策略与现有的大规模电子生产方法不兼容。

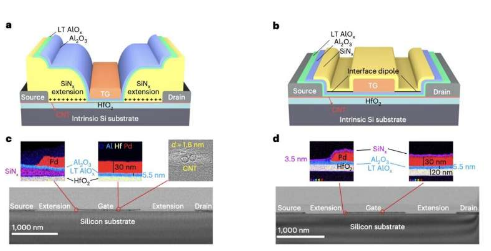

加州大学圣地亚哥分校和台积电的研究人员最近开发了具有局域固态扩展掺杂的新型碳纳米管金属氧化物半导体场效应晶体管(MOSFET)。NatureElectronics中提出的这些晶体管实现了卓越的性能,而且可以使用与现有互补金属氧化物半导体(CMOS)掺杂工艺兼容的策略来有利地控制它们的极性。

“我们报告了顶栅互补碳纳米管MOSFET,其中使用局部共形固态延伸掺杂来设置器件极性并实现性能匹配,”ZichenZhang、MatthiasPasslack及其同事告诉TechXplore。

“晶体管的沟道保持未掺杂,提供互补金属氧化物半导体兼容的n和p-MOSFET阈值电压,分别为+0.29V和-0.25V。与代工厂兼容的制造工艺在扩展中实现了局部电荷转移来自n型器件的氮化硅(SiNx)中的缺陷水平或p型器件的SiNx/氧化铝(Al2O3)界面处的静电偶极子。”

研究人员在一系列测试中测试了基于碳纳米管的设备原型。他们还将这些实验的结果与为未来可扩展MOSFET设定的要求进行了比较。

尽管研究人员仍处于其提出的晶体管的开发和测试的早期阶段,但他们已经取得了非常有希望的结果。值得注意的是,这些晶体管的性能与之前报道的其他基于低维半导体的MOSFET相当,但它们也与现有CMOS技术兼容,因此未来更容易升级。

Zang、Passlack及其同事在论文中写道:“我们观察到SiNx施主缺陷密度接近5×1019 cm-3,这可以在按比例缩放的纳米管器件的扩展中维持0.4nm-1的碳纳米管载流子密度。”“我们的技术可能适用于其他先进的场效应晶体管沟道材料,包括二维半导体。”

该团队创建的新型晶体管可能有助于未来创建基于一维碳纳米管的更小、高性能和可扩展的电子产品。研究人员计划继续改进和测试他们的晶体管,希望在2031年完成他们的设计。

研究人员在论文中总结道:“我们制造了顶栅互补CNTMOSFET,器件的极性是通过局部共形固态扩展掺杂来设置的,性能匹配是与CMOS代工资源兼容的模块。”“仅将掺杂局部化到扩展区是该方法的一个重要方面,并且减少了短沟道器件中器件间的变异性,因为掺杂剂波动是变异性的重要来源。”

免责声明:本文由用户上传,与本网站立场无关。财经信息仅供读者参考,并不构成投资建议。投资者据此操作,风险自担。 如有侵权请联系删除!

-

【木地板材料】木地板是一种广泛应用于家居和商业空间的地面装饰材料,因其自然美观、耐用性强、环保性好等特...浏览全文>>

-

【木地板安装】木地板安装是一项需要细致规划和专业操作的工程,无论是新房装修还是旧房翻新,选择合适的木地...浏览全文>>

-

【木的组词怎么写】在汉语学习中,词语的积累和运用是非常重要的部分。对于“木”这个字来说,它不仅是常见的...浏览全文>>

-

【木的象形字有哪些字】在汉字的发展过程中,许多字最初都是通过象形的方式创造出来的,用来表示具体的事物。...浏览全文>>

-

【木岛法子介绍】木岛法子(Kazuko Kikuchi)是日本著名演员、模特及艺人,以其在影视作品中的出色表现和独特...浏览全文>>

-

【木代尔是什么面料】“木代尔是什么面料”是许多消费者在选购衣物时常常会提出的问题。木代尔是一种天然纤维...浏览全文>>

-

【木代尔和莫代尔哪种面料好】在选择衣物面料时,很多人会遇到“木代尔”和“莫代尔”这两个名称,容易混淆它...浏览全文>>

-

【萝卜的营养价值】萝卜是一种常见的根茎类蔬菜,不仅味道清脆爽口,还具有丰富的营养价值。无论是生吃、炒食...浏览全文>>

-

【萝卜的药用功效和作用】萝卜,作为日常生活中常见的蔬菜之一,不仅味道清脆、营养丰富,还具有多种药用价值...浏览全文>>

-

【萝卜的家常做法】萝卜是一种非常常见的蔬菜,不仅价格实惠,而且营养丰富,适合多种烹饪方式。无论是炖、炒...浏览全文>>